|   |   |   |   |   | Disable Function    |

|---|---|---|---|---|---------------------|

| Х | х | X | x | 1 | Data Bus Tri-stated |

| 1 | 1 | 0 | 1 | 0 | Illegal Condition   |

| х | x | 1 | 1 | 0 | Data Bus Tri-stated |

Table 9.1 Port and register select signals summary

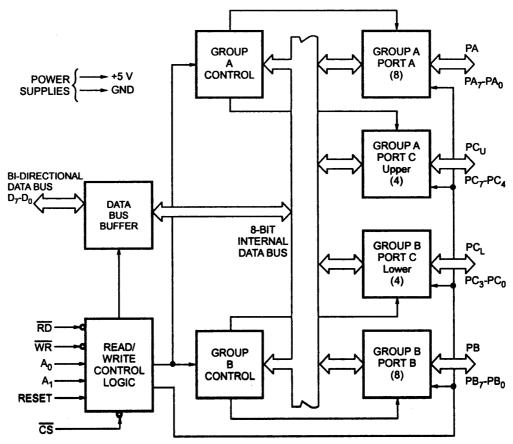

## 9.3 Block Diagram

Fig. 9.2 shows the internal block diagram of 8255A. It consists of data bus buffer, control logic and Group A and Group B controls.

Fig. 9.2 Block diagram of 8255A

#### 9.3.1 Data Bus Buffer

This tri-state bi-directional buffer is used to interface the internal data bus of 8255 to the system data bus. Input or Output instructions executed by the CPU either Read data from, or Write data into the buffer. Output data from the CPU to the ports or control register, and input data to the CPU from the ports or status register are all passed through the buffer.

| Reset                             | This is an active high input used to reset 8255. When RESET input is high, the control register is cleared and all the ports are set to the input mode. Usually Reset Out signal from 8085 is used to reset 8255.                                                                                                                                                                                                                                                          |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> and A <sub>1</sub> | These input signals along with $\overline{RD}$ and $\overline{WR}$ inputs control the selection of the control/status word registers or one of the three ports. Table. 9.1 summarizes the status of $A_0$ , $A_1$ , $\overline{CS}$ , $\overline{RD}$ and $\overline{WR}$ to access the control word/ports. $A_0$ and $A_1$ are generally connected to the $A_0$ , $A_1$ pins of the address bus; the 8255 therefore occupies four consecutive locations in the I/O space. |

Fig. 9.1 Pin diagram of 8255A

| A <sub>1</sub> | A <sub>0</sub> | RD | WR | C8 | Operations                   |

|----------------|----------------|----|----|----|------------------------------|

|                | İ              |    |    |    | Input (Read) Operation       |

| 0              | 0              | 0  | 1  | 0  | Port A to Data Bus           |

| 0              | 1              | 0  | 1  | 0  | Port B to Data Bus           |

| 1              | 0              | 0  | 1  | 0  | Port C to Data Bus           |

|                |                |    |    |    | Output (Write) Operation     |

| 0              | 0              | 1  | 0  | 0  | Data Bus to Port A           |

| 0              | 1              | 1  | 0  | 0  | Data Bus to Port B           |

| 1              | 0              | 1  | 0  | 0  | Data Bus to Port C           |

| 1              | 1              | 1  | 0  | 0  | Data Bus to Control Register |

## 9.3.2 Control Logic

The control logic block accepts control bus signals as well as inputs from the address bus, and issues commands to the individual group control blocks (Group A control and Group B control). It issues appropriate enabling signals to access the required data/control words or status word. The input pins for the control logic section are described here.

# 9.3.3 Group A and Group B Controls

Each of the Group A and Group B control blocks receives control words from the CPU and issues appropriate commands to the ports associated with it. The Group A control block controls Port A and  $PC_7 - PC_4$  while the Group B control block controls Port B and  $PC_3-PC_0$ .

- Port A: This has an 8-bit latched and buffered output and an 8-bit input latch. It can be programmed in three modes: mode 0, mode 1 and mode 2.

- Port B: This has an 8-bit data I/O latch/ buffer and an 8-bit data input buffer. It can be programmed in mode 0 and mode 1.

- Port C: This has one 8-bit unlatched input buffer and an 8-bit output latch/buffer. Port C can be splitted into two parts and each can be used as control signals for ports A and B in the handshake mode. It can be programmed for bit set/reset operation.

### 9.4 Operation Modes

### 9.4.1 Bit Set-Reset (BSR) Mode

The individual bits of Port C can be set or reset by sending out a single OUT instruction to the control register. When Port C is used for control/status operation, this feature can be used to set or reset individual bits.

#### 9.4.2 I/O Modes

## Mode 0: Simple input/output.

In this mode, ports A and B are used as two simple 8-bit I/O ports and Port C as two 4-bit ports. Each port (or half - port, in case of C) can be programmed to function as simply an input port or an output port. The input/output features in Mode 0 are as follows:

- 1. Outputs are latched.

- 2. Inputs are buffered, not latched.

- 3. Ports do not have handshake or interrupt capability.

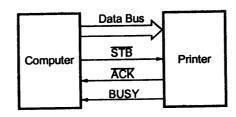

Fig. 9.3 Data transfer between computer and printer using handshaking signals

# Mode 1: Input/Output with handshake

In this mode, input or output data transfer is controlled by handshaking signals. Handshaking signals are used to transfer data between devices whose data transfer speeds are not same. For example, computer can send data to the printer with large speed but printer can't accept data and print data with this rate. So computer has to send data with the speed with which printer can accept. This type of data transfer is achieved by using handshaking signals alongwith data signals. Fig. 9.3 shows data transfer between computer and printer using handshaking signals.

These handshaking signals are used to tell computer whether printer is ready to accept the data or not. If printer is ready to accept the data then after sending data on data bus, computer uses another handshaking signal (STB) to tell printer that valid data is available on the data bus.

The 8255 mode 1 which supports handshaking has following features.

- Two ports (A and B) function as 8-bit I/O ports. They can be configured either as input or output ports.

- 2. Each port uses three lines form Port C as handshake signals. The remaining two lines of Port C can be used for simple I/O functions.

- 3. Input and output data are latched.

- 4. Interrupt logic is supported.

# Mode 2: Bi-directional I/O data transfer

This mode allows bi-directional data transfer (transmission and reception) over a single 8-bit data bus using handshaking signals. This feature is available only in GroupA with Port A as the 8-bit bi-directional data bus; and PC<sub>3</sub>-PC<sub>7</sub> are used for handshaking purpose. In this mode, both inputs and outputs are latched. Due to use of a single 8-bit data bus for bi-directional data transfer, the data sent out by the CPU through Port A appears on the bus connecting it to the peripheral, only when the peripheral requests it. The remaining lines of Port C i.e. PC<sub>0</sub>-PC<sub>2</sub> can be used for simple I/O functions. The Port B can be programmed in mode 0 or in mode 1. When Port B is programmed in mode 1, PC<sub>0</sub>-PC<sub>2</sub> lines of Port C are used as handshaking signals.